开关电源EMC设计-电巢学堂

开关电源的设计有三大难题,可能会导致设计在最后一刻功败垂成,那就是热问题、安规问题和电磁干扰。其中,电磁干扰问题是最难被预测的,并且受时间约束(测试费用昂贵,且按小时计费)。

电磁干扰像一个“气球”,若试图在某一频率“压下”,可能会在另一频率“鼓起”。在设法符合了传导发射之后,可能会发现辐射限制又超标了,诸如此类。

电磁干扰是开关电源设计中公认的最具挑战性的领域,许多非特征性寄生参数会对测试结果产生影响,因此需要投入大量的人为调整(连蒙带猜、又凑又碰、死马当活马医)。当然,如果对开关电源的原理有清晰而深刻的理解,并且在设计阶段把关键因素考虑进去,那么在电磁干扰测试和调试过程中,主体部分便无需重新设计,避免功亏一篑的“灾难”发生。

电磁干扰现象的发生

任何天线既是良好的接收器,又是良好的发射器。有些情况下,从输出电缆开始辐射,然后被输入电缆(通过辐射)接收,并从该点传导给建筑的配电网(再次辐射)。输入和输出电缆线经常携带大量的高频电磁噪声,在辐射频谱和传导频谱中都能看到。

麦克斯韦方程组表明,时变电场(E,量纲V/m)产生时变磁场(H,量纲A/m),反之亦然。电场E和磁场H同时存在,与原始磁源和电源之间存在时间差。电磁场在一定距离外组合成电磁波并以光速在空间传播。

极远距离处的电磁场相互成正比,能够形成自我维持且远距离传播的电磁波(甚至穿越银河系)。如果电磁波的一个分量(电场或磁场)遭到破坏,那么整个电磁波将不复存在。因此,远场常用射频屏蔽或电磁屏蔽,抑制缓变的电磁场和(或)近场,常用静电屏蔽和(或)磁屏蔽。

电路的场有如下四种基本类型:(1)静电场:电荷的固定分布,电荷不能移动,无法形成电流(2)静磁场:由直流回路产生,与静电场成对偶关系。恒定磁场H不随时间变化,场信息无法传播(3)时变电场(4)时变磁场。

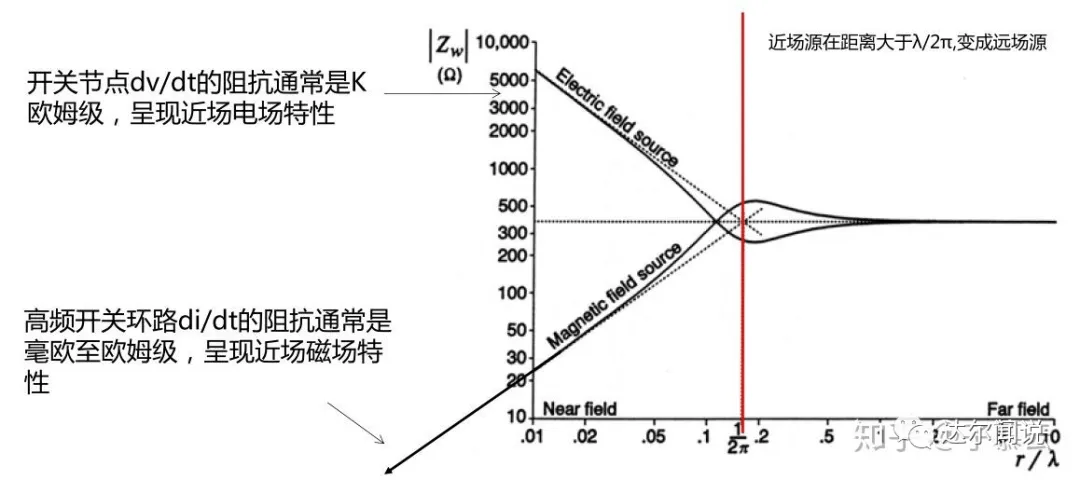

电场E和磁场H的比值成为波阻抗。PCB上一个小环形电流回路就能产生磁场,而电压跳变的铜条或金属条就能形成电场源(例如散热器)。一旦场随时间变化,磁场就能产生相应的电场,电场也能产生相应的磁场。距离很远时,电场与磁场互成正比,并形成电磁波。远场和近场的边界定义为距电磁干扰源约1/6波长处,即0.16波长处。近场的磁场和电场对空间辐射的能量很小,能量主要集中在近场范围内。

图1 自由空间的电磁阻抗

DC/DC电路的EMC问题

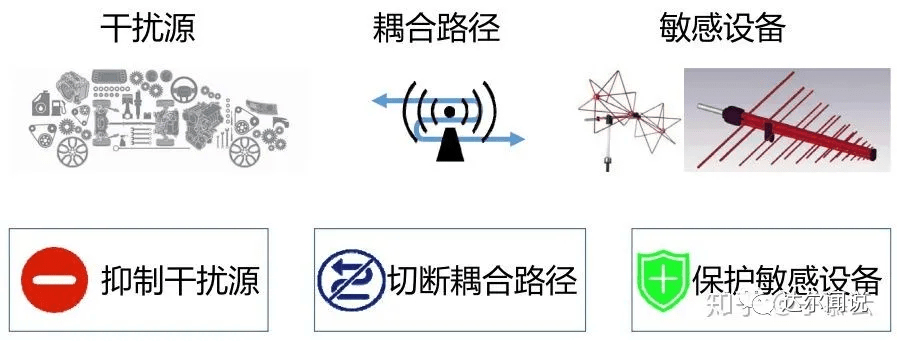

影响EMC性能有三大要素,分别是干扰源、耦合路径和敏感设备。

图2 影响EMC的三大要素

1)噪音源

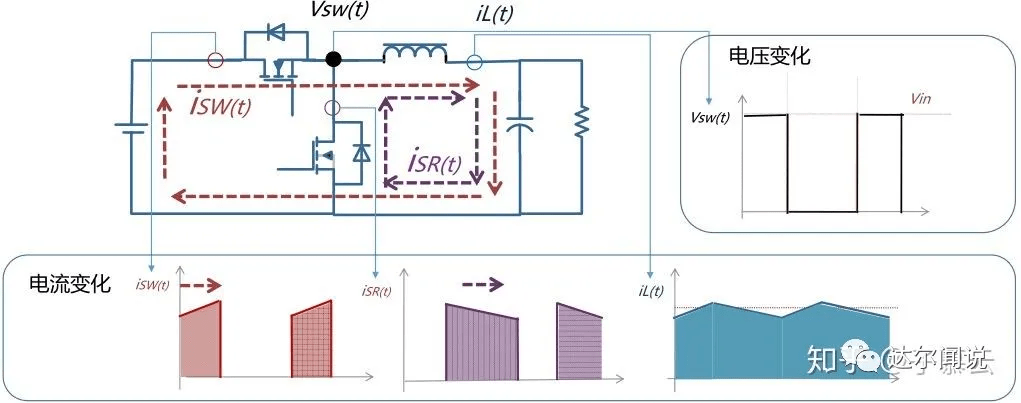

以BUCK为例,DC/DC芯片开关过程中产生电压和电流的变化,包含了较快的di/dt和dv/dt噪声分量,这是噪音源。

图3 BUCK电路的常见开关波形

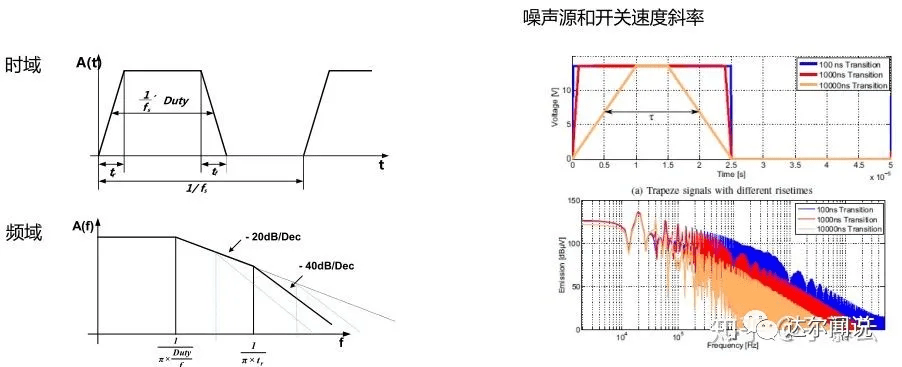

图4 开关波形的斜率与噪音衰减的关系

以BUCK为例,DC/DC芯片的开关噪声的开关斜率越小,高频噪声的分量衰减就越大。

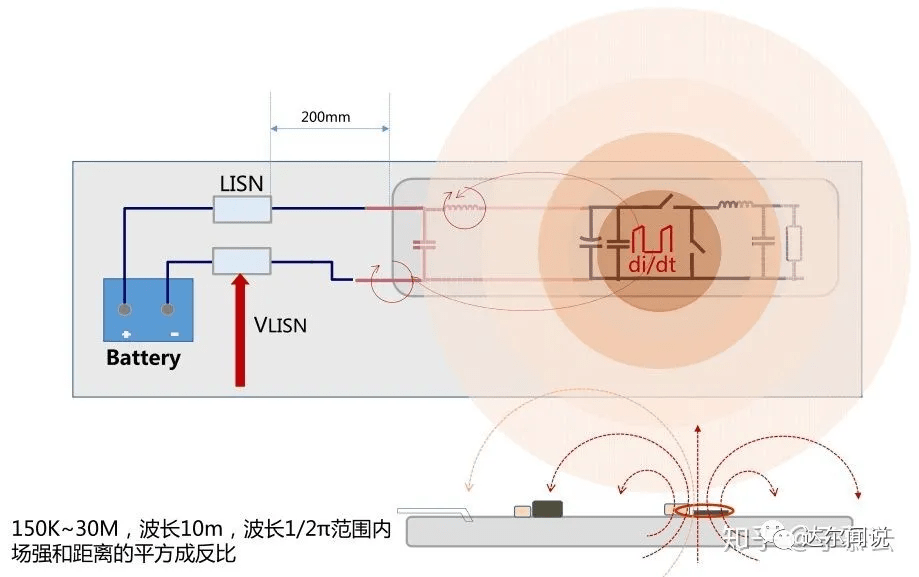

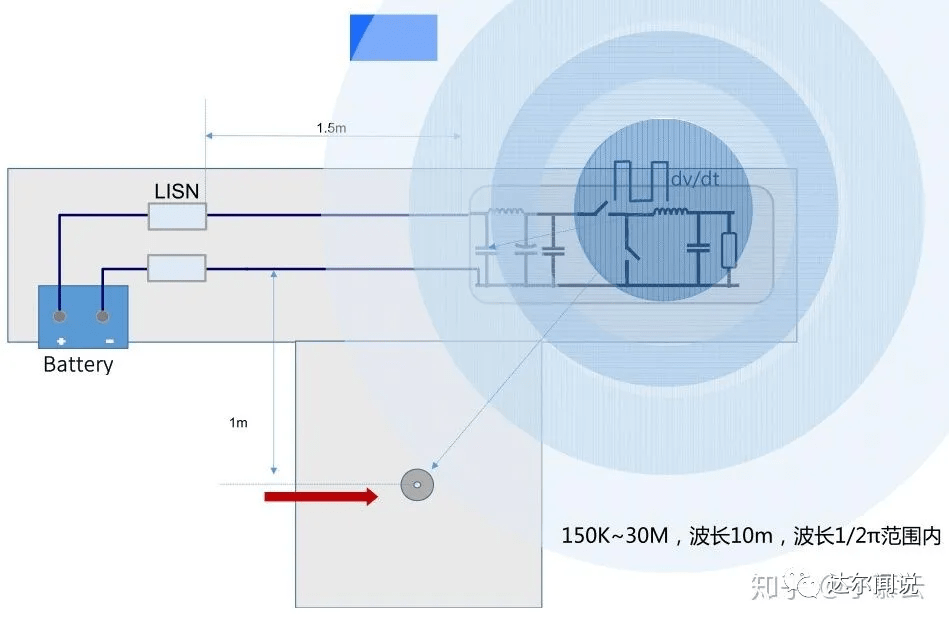

2)传播路径

EMC噪音以传导和空间辐射的形式对外辐射。阻断空间辐射的最好方式是做好金属屏蔽,而传导则比较麻烦,噪音会以磁场和电场的形式耦合到附件的器件和PCB走线上,然后通过连接器传到线束上,然后导致空间辐射或者传导超标。

图5 传导中常见近场磁场的干扰

图6 传导中常见近场电场的干扰

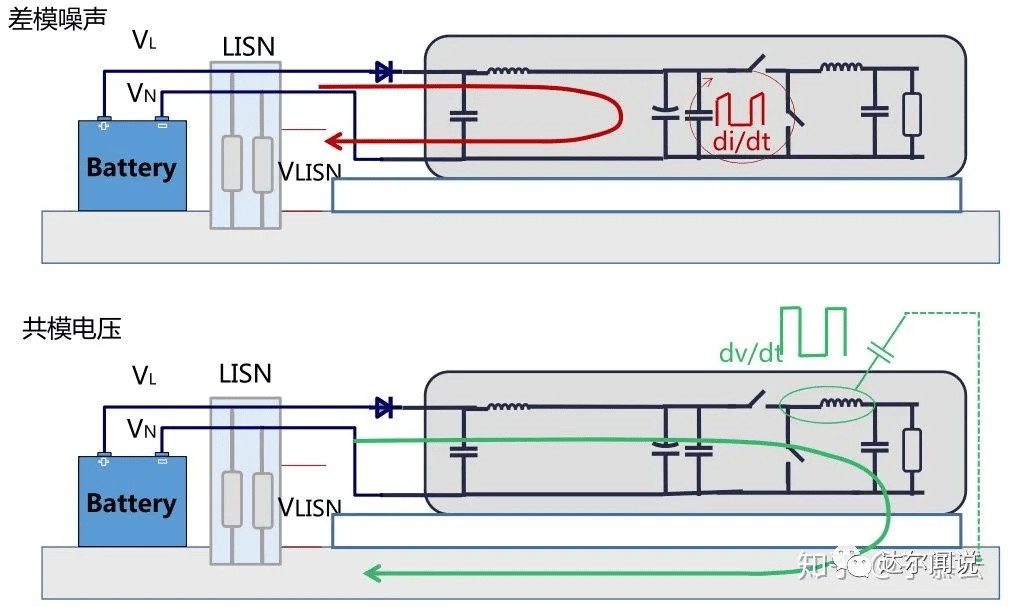

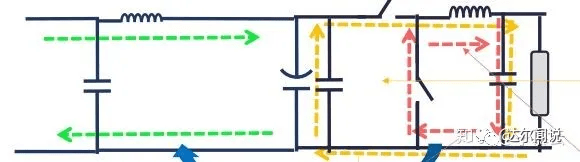

传导发射可基本分为两类:

(1)差模(DM),也称为对称模式或普通模式

(2)共模(CM),也称为非对称模式或接地泄露模式

图7 差模和共模噪音

共模噪音的产生是由于PCBA与机壳之间存在着容性耦合,电路上的高频电压跳变会通过容性耦合通过机壳导入(泄露)大地,所以在线束上被测试到共模噪音。同时,共模噪音会把长输出电缆作为巨型天线。从共模噪音的产生机理中,我们也可以推断出共模电流频率通常要比差模电流频率高很多。因此,它有能力产生强烈的辐射。如果线路阻抗不相等,共模噪音会转化为差模噪音,从源头控制噪音很重要。

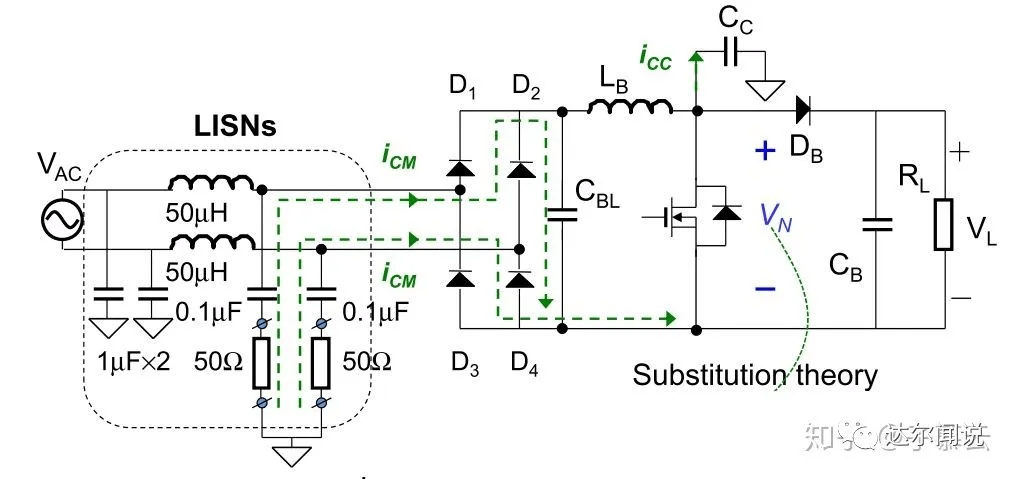

测量电磁干扰要用到阻抗稳定网络(ISN)。在离线电源中,它称为线路阻抗稳定网络(LISN),也称为人工电源网络(AMN)。它的作用是阻挡一切来自电网对外部噪声进入测试区域,为待测装置提供纯净的测试环境;同时,也阻止电源噪声进入电网,将其转入测试区域。

图8 传导发射测试时的人工网络(LISN)

将机器的金属外壳接地的目的是防止装置内辐射外泄。金属外壳也常被用作良好的散热器,这样的后果是内部子系统或电路与金属机壳之间产生了泄露路径(阻性或容性),即使泄露电流很小也足以产生电磁干扰的问题。但是,如果这些泄露电流不能以某种方式排放,外壳将充电至不可预测且不确定的电压,并最终辐射出去(电偶极子或电场源)。也就是说,未接地的外壳会感应并再次辐射内部强电场或强磁场。即使没有功率器件安装在外壳上,内部电路与外壳之间也会有其他泄露路径,所以外壳接地不可避免。

Layout设计对EMC的影响

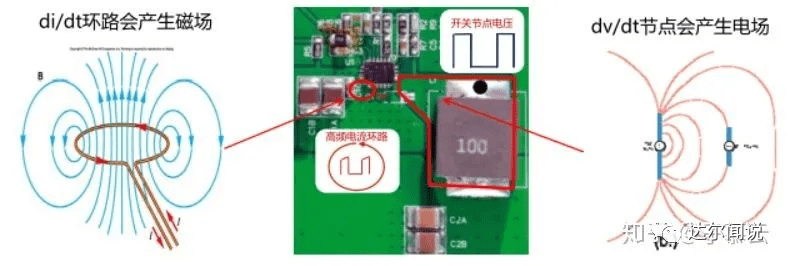

1)DC/DC电源的两大噪音源:DC/DC芯片的主要噪声源是高频电流环路(Hot loop)和高频开关节点(SW note), 包含了比较宽频段的谐波分量。

图9 DC/DC 的两大噪音源

2)高频电流环路(Hot loop)和高频开关节点(SW note)分别产生交变的磁场和电场。高频电流环路形成的磁场大小取决于环路面积和电流大小。磁场强度随着电流和环路面积而增大。

图10 DC/DC 的两大噪音源

3)在设计开关电源的PCB时,切记,必须使电压跳变的铜面积(例如交换节点处)最小化,同时减小所有电流回路包围的面积,特别是含有高频谐波的回路。

图11 减小节点面积相当于减小等效的耦合电容,有助于减小共模电流

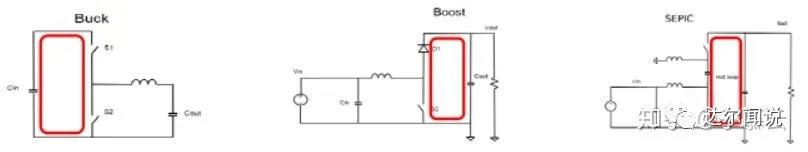

4)在Layout设计时,对各种拓扑的高频电流环路需要了然于心。高频电流环路存在于开关回路和滤波电容之间,电感电流是连续的三角波波形,相对而言不是关注的重点。高频电流环路主要存在于电流切换的支路,开关管和连接在开关端两端的电容组成了高频电流回路。

图12 各种拓扑的高频电流环路

接着,减少高频电流回路面积是设计时重点关注和采取的措施,以BUCK为例:

a)尽量使用同步Buck方案减少高频电流回路面积。

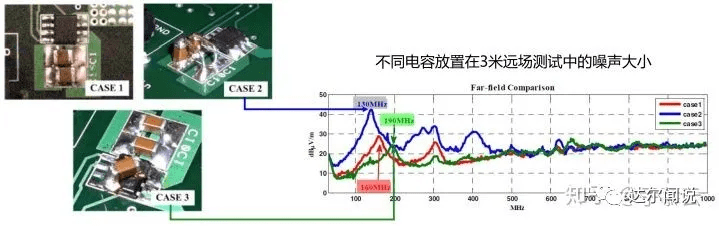

b)输入电容靠近开关管放置。电容要尽可能的靠近开关管,同步buck芯片的输入电容要靠近芯片放置。

图13 不同的电容放置方法导致,高频环路的环路大小不一样,环路越小,磁场能量越小

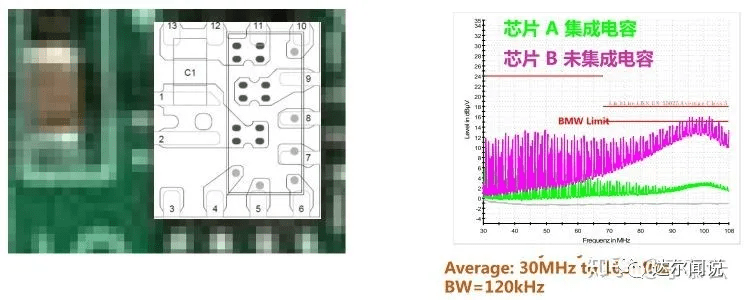

c)芯片内部集成电容,通过芯片内部集成电容的方式,进一步减小电容,Linear和MPS已有相应的方案。芯片集成电感对EMI有巨大的帮助,可以极大的减小近场磁场能量,对传导和辐射都有很好的改善。

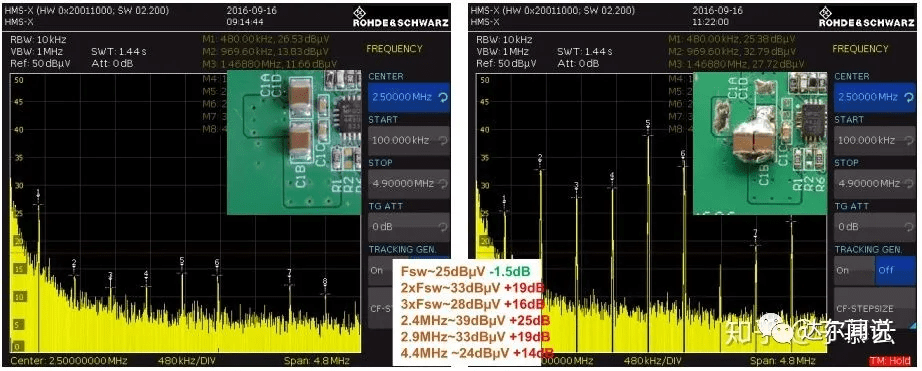

图14 MPS集成电容的电源方案的EMC测试

d)对称放置输入电容抵消磁场:

图15 采用对称电容设计的电路,磁场抵消后辐射能量减弱

e)高频电流环路底层完整PCB铺铜

减少电磁干扰最有效和性价比最高的方法是覆铜,但是必须尽可能保证覆地层的完整性。切记,低频时的返回电流总是试图按照最短的直线路径流动。但高频时的返回电流(或开关波形中的高次谐波)总是试图直接按照自己的前进轨迹(在对面层)流动。因此,一旦有机会,电流将自动按照包围面积最小的路径流动。该路径自感最小,回路阻抗最低(回路阻抗在低频呈阻性,但在高频段呈感性)。所以,若对覆地层的分割考虑不周(可能为了方便布线),功率变换器的返回电流就会被其中的分割线分流,从而在PCB板上形成有效的缝隙天线。

图16 高频电流环路底层完整PCB铺铜

完整的地平面可以感应出电流,并形成相反的磁场来抵消高频环路带来的磁场。完整的铺铜距离高频环路越近,对磁场的削弱作用越强。

图17 不同距离铺铜的磁场强度

5)电感挖地会破坏完整的地

图18 电感挖地会破坏完整的地

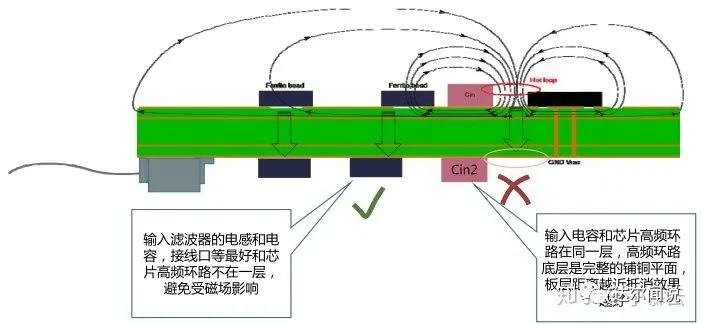

6)输入滤波器远离高频电流环路。

图19 输入滤波器远离高频电流环路

注意,输入端滤波器位置的摆放,远离高频电流环路。

7)避免功率地和输入地的耦合:输入和输出电容的地汇集至一点,使得电源模块是一个整体。

图20 避免功率地和输入地的耦合

开关电源的EMC设计建议

(一)、器件选型

改善EMC性能,拓扑和器件选型很重要,选型恰当可“事半功倍”。

选择恰当的拓扑:在设计系统电源架构时,平衡成本及设计难度的前提下,规避使用EMC性能比较难驾驭的拓扑结构,比如SPEIC的EMC性能调试较有难度。BUCK-BOOST电路在输入和输出接近时,系统也容易不稳定。

芯片选型:可以参考下列要点,芯片设计难度高,下列要点只是强调几个方面的要点,不是设计的准则,选型需要考虑的因素比较多,譬如成本考量、功能要求、电源架构的延续与继承,等等。

(1)使用同步类型DC/DC芯片

(2)使用高集成度的电源方案,譬如集成MOSFET的Buck Convertor,二合一的BUCK,等。

(3)FPWM选项:在电源效率符合要求的前提下,配置为FPWM(Force PWM,强制PWM模式)。电源的轻载模式,因为开关频率的不固定,对EMC性能有较大的副作用。

(4)外部时钟同步(External SYNC)选项:可配置外部同步时钟的电源芯片,留了一个通过软件转移EMC超标频点的可能。不过,这个功能的主要目的是应对电源对AM模块的干扰,对EMC的实际效果需要根据实际情况而定。

(5)展频(Spread Spectrum)选型:对开关信号的展频对EMC的性能改善有直接的帮助。但是,需要注意的是,展频选项和第(4)条的外部时钟选项是冲突的,外部时钟同步的优先级更高。当外部时钟被使能,展频(Spread Spectrum)将自动关闭。

外围器件选型:电源模块的外围器件的选型对EMC的性能影响也很大,特别是电感。在设计成本可以被平衡的前提下,尽量选用一体成型的屏蔽电感,避免选用旧式的组装电感,磁场会从空隙里渗漏出来。

磁封胶电感是平衡成本与性能的一个不错的选择,但是磁封胶电感的漏磁仍然是比较明显的。在选择磁封胶电感时,可以考量以下两个要点:电感的厚度:电感越薄,漏磁的辐射范围越小,对EMC性能越有帮助;布线时注意磁封胶电感的管脚处裸露的铜线对磁场的泄露。

(二)、原理图设计

1)平衡电源效率及其它要求的前提下,尽可能配置成FPWM(Force PWM)模式;

2)低频开关频率有利于EMC性能但是会导致外围器件的尺寸,主要是电感和输出电容;

3)开关频率的选择还需要考虑对AM及其它频率敏感的模块的干扰;

4)控制芯片输入端必须放置Bypass电容,推荐容值为100nF,在Layout时靠近芯片管脚摆放;

5)预留Snubber电路,等PCBA回来时实际调试;

(三)、Layout设计

1)首先,识别大电流回路,包括输入部分的大电流回路和输出部分的大电流回路。大电流流经的路径一般会注意的,比如铺设电源平面,加粗走线,等等。

在这些常规操作之外,比较容易忽视的是回流路径(俗称“地”)的处理,这像一个城市的下水道,不呈现在面上的设计才是真的考验。关于地的设计,后续细述。

2)接着,保护好敏感信号,譬如环路补偿电路、电压反馈,等。在复杂的电源设计中,可以根据规格书的建议并在它的指导之下把敏感信号进行分地。这里所谓的“分地”是指把敏感信号的回流路径连接到一起,然后统一接入功率地。

注意:保证电源模块的地平面完整,不要进行人为割裂,譬如这是信号地平面,这是功率地平面,不但是一厢情愿,而且容易弄巧成拙,因为开关电源里的噪音包括开关信号的噪音以及电感的漏磁,都需要尽可能完整的地平面来吸收,所以地平面不能割裂。

3)确保大电流回路的面积最小,高频di/dt回路是大电流回路之中最关键的一环,所以优先保证高频di/dt回路的面积最小。Buck电路的高频di/dt回路是输入回路,Boost电路的高频di/dt是输出回路。

4)高频dv/dt节点是电感与控制芯片或者MOSFET相连接的那个节点,这个节点产生的高频dv/dt会耦合到机壳或散热片,通过机壳将一部电“漏走”,导致共模噪音。

5)确保Bypass电容(~100nF)靠近放置于控制芯片的电源输入管脚处,并且在同一面,因为过孔会产生寄生电感,从而引起过冲,可能导致芯片工作异常。

6)Snubber电路靠近控制芯片的开关节点。如果是异步拓扑,Snubber电路靠近肖特基二极管;如果是功率MOSFET是外置的,Snubber电路靠近MOSFET。